Какая из шин процессора является однонаправленной

Содержание

Из каких шин состоит системная магистраль?

Из каких шин состоит системная магистраль?

Системная магистраль включает в себя три многоразрядные шины:

– шину данных – служит для пересылки данных между ЦП и памятью или ЦП и устройствами ввода/вывода.

– шину адреса – служит для выбора устройств или ячеек памяти, куда пересылаются или откуда считываются данные по шине данных. Однонаправленная шина.

– шину управления – служит для передачи управляющих сигналов, определяющих характер обмена информацией по магистрали, предназначенных памяти и устройствам ввода/вывода.

В чем заключается модульный подход к построению ЭВМ?

В основу архитектуры современных персональных компьютеров положен модульный принцип. Он позволяет потребителю самому комплектовать нужную ему конфигурацию компьютера и производить при необходимости ее модернизацию. Модульная организация компьютера опирается на магистральный (шинный) принцип обмена информацией между модулями. Обмен информацией между отдельными устройствами компьютера производится по трем многоразрядным шинам, соединяющим все модули: шине данных, шине адресов и шине управления.

Что такое магистральный способ обмена информацией?

Магистральный способ обеспечивает обмен информацией между функциональными и конструктивными модулями различного уровня с помощью магистралей, объединяющих входные и выходные шины.

Различают одно-, двух-, трех- и многомагистральные связи.

Что такое микропрограммируемость?

Микропрограммируемость – это способ реализации принципа программного управления. Суть его состоит в том, что принцип программного управления распространяется и на реализацию устройства управления. Другими словами, устройство управления строится точно так же, как и весь компьютер, только на микроуровне, т.е. в составе устройства управления имеется своя память, называемая управляющей памятью или памятью микрокоманд, свой «процессор», свое устройство управления.

Как выглядит архитектура ЭВМ с одношинной структурой?

Одношинная архитектура – архитектура микропроцессорной системы с общей памятью данных и команд и общей шиной для обмена с памятью.

Чтение кодов команд из памяти системы производится с помощью циклов чтения. Поэтому в случае одношинной архитектуры на системной магистрали чередуются циклы чтения команд и циклы пересылки (чтения и записи) данных, но протоколы обмена остаются неизменными независимо от того, что передается – данные или команды. В одношинной архитектуре для связи с памятью и ВУ используется одна и та же шина.

Как выглядит архитектура ЭВМ с многошинной структурой?

Основная особенность такой архитектуры состоит в том, что для каждого способа обмена информацией с ПУ используется отдельная группа шин: отдельные шины для программного режима обмена информации с прерываниями или без прерываний и для ввода-вывода информации в режиме прямого доступа к памяти, которые передают блоки данных с большой скоростью.

Протоколы обмена данными, структура шин и быстродействие при обмене для каждой из групп шин могут, оптимальным образом, адаптированы к ПУ в соответствии с выбранным методом.

Из чего состоит машина фон Неймана?

Машина Фон Неймана состоит из памяти, устройств ввода/вывода и центрального процессора (ЦП). Центральный процессор, в свою очередь, состоит из устройства управления (УУ) и арифметико-логического устройства (АЛУ)

Обобщенный алгоритм функционирования ЭВМ фон Неймана.

– С помощью внешнего устройства в память компьютера вводится программа.

– Устройство управления считывает содержимое ячейки памяти, где находится первая инструкция (команда) программы и организует ее выполнение. Команда может задавать:

– – выполнение логических или арифметических операций;

– – чтение из памяти данных для выполнения арифметических или логических операций;

– – запись результатов в память;

– – ввод данных из внешнего устройства в память;

– – вывод данных из памяти на внешнее устройство.

– Устройство управления начинает выполнение команды из ячейки памяти, которая находится непосредственно за только что выполненной командой. Однако этот порядок может быть изменен с помощью команд передачи управления (перехода). Эти команды указывают устройству управления, что ему необходимо продолжить выполнение программы, начиная с команды, содержащейся в иной ячейки памяти.

– Результаты выполнения программы выводятся на внешнее устройство компьютера.

– Компьютер переходит в режим ожидания сигнала от внешнего устройства.

Многошинная структура ЭВМ. Достоинства, недостатки.

Основная особенность ее организации состоит в том, что для каждого способа обмена информацией с ПУ используется отдельная группа шин: отдельные шины для программного режима обмена информации с прерываниями или без прерываний и для ввода-вывода информации в режиме прямого доступа к памяти, которые передают блоки данных с большой скоростью. Протоколы обмена данными, структура шин и быстродействие при обмене для каждой из групп шин могут, оптимальным образом, адаптированы к ПУ в соответствии с выбранным методом.

Недостатками же являются большая сложность, чем у одношинной структуры и меньшая стандартизация шин.

Одношинная структура ЭВМ. Достоинства, недостатки.

В этом случае блоки ЭВМ объединяются посредством одной группы шин, в которую входят подмножества шин данных, адреса и управляющих сигналов. При такой организации системы шин обмен информацией между процессором, периферийными устройствами и памятью выполняется по единому правилу, отдельные команды ввода-вывода для обращения к ПУ в системе команд отсутствуют. Это позволяет повысить гибкость и эффективность ЭВМ, так как весь набор команд обращения к памяти может использоваться для передачи и обработки содержимого регистров ПУ. Кроме того, другим важным достоинством является простота структуры шин и минимизация числа связей для обмена информацией между устройствами ЭВМ.

Недостатками являются: наличие медленных устройств на шине, ограничение на одновременный обмен данными (не более двух устройств одновременно).

13. Перечислите требования, предъявляемые к современным ЭВМ.

Требования к современным ЭВМ такие:

– Отношение стоимости к производительности.

– Надежность и отказоустойчивость.

– Совместимость и мобильность ПО.

Что такое надежность?

Надежность ЭВМ — это способность машины сохранять свои свойства при заданных условиях эксплуатации в течение определенного промежутка времени. Количественной оценкой надежности ЭВМ, содержащей элементы, отказ которых приводит к отказу всей машины, могут служить следующие показатели:

– вероятность безотказной работы за определенное время при данных условиях эксплуатации;

– наработка ЭВМ на отказ;

– среднее время восстановления машины и др.

15. Чем понятие “надежность” отличается от понятия “отказоустойчивость”?

В отличие от надежности – способности машины сохранять свои свойства при заданных условиях эксплуатации в течение определенного промежутка времени, отказоустойчивость — это свойство машины сохранять свою работоспособность после отказа одного или нескольких составных компонентов. Отказоустойчивость определяется количеством любых последовательных единичных отказов компонентов, после которого сохраняется работоспособность системы в целом.

Что такое масштабируемость?

Масштабируемость характеризует способность ЭВМ плавно увеличивать вычислительную мощность без деградации производительности ЭВМ в целом. Система называется масштабируемой, если она способна увеличивать производительность пропорционально дополнительным ресурсам.

Что такое совместимость?

Под аппаратной совместимостью понимают способность одного устройства логически заменять другое устройство того же типа или способность одного устройства как физически, так и логически сопрягаться с другими. В последнем случае в качестве синонимов аппаратной совместимости используются также термины «полная (аппаратная) совместимость» и «совместимость по разъемам».

Под программной совместимостью одной ЭВМ с другой понимают способность первой выполнять программы, которые были разработаны для второй ЭВМ. Различные модели одного и того же семейства ЭВМ имеют, как правило, «одностороннюю» совместимость, поскольку компьютеры более поздних (старших) моделей обычно являются более мощными (т.е. способны исполнять дополнительные команды, имеют больший объем памяти и т.д.). В этом случае говорят, что ЭВМ старшей модели совместима снизу вверх с ЭВМ младшей модели, подчеркивая тот факт, что первая может выполнять программы, подготовленные для второй, но не наоборот.

Что такое Х-терминалы?

X-терминал — это выделенное аппаратное обеспечение, на котором выполняется X-сервер и которое служит в качестве тонкого клиента. Они удобны в случаях, в которых множество пользователей одновременно используют один большой сервер приложений.

Что такое мейнфрейм?

Мейнфрейм (Большая универсальная ЭВМ) — высокопроизводительный компьютер со значительным объёмом оперативной и внешней памяти, предназначенный для организации централизованных хранилищ данных большой ёмкости и выполнения интенсивных вычислительных работ. Мейнфреймы обычно применяются для целочисленных операций, требовательных к скорости обмена данными, к надёжности и к способности одновременной обработки множества процессов.

Тесты фирмы SPEC.

Основным результатом работы SPEC являются наборы тестов. Эти наборы разрабатываются SPEC с использованием кодов, поступающих из разных источников. SPEC работает над портированием этих кодов на разные платформы, а также создает инструментальные средства для формирования из кодов, выбранных в качестве тестов, осмысленных рабочих нагрузок. Поэтому тесты SPEC отличаются от свободно распространяемых программ

В настоящее время имеется два базовых набора тестов SPEC, ориентированных на интенсивные расчеты и измеряющих производительность процессора, системы памяти, а также эффективность генерации кода компилятором. Как правило, эти тесты ориентированы на операционную систему UNIX, но они также портированы и на другие платформы. Процент времени, расходуемого на работу операционной системы и функции ввода/вывода, в общем случае ничтожно мал.

Функциональная схема ПЗУ.

Классификация ПЗУ.

– Электрически одноразово программируемое ПЗУ

– Репрограммируемое (РПЗУ, ППЗУ)

54. Физические основы запоминающего элемента однократно программируемого ПЗУ (схема).

Когда перемычка есть, через транзистор проходит ток и считывается высокий уровень. Если Uп высокое, то при открытии транзистора ток пережигает проволоку.

55. Физические основы запоминающего элемента репрограммируемого ПЗУ (схема).

В перезаписываемом ПЗУ используется магнитно-индукционный МОП-транзистор с плавающим затвором.

56. Назначение и устройство ПЛМ (схема).

ПЛМ представляет собой функциональный блок, созданный на базе полупроводниковой технологии и предназначенных для реализации логических функций цифровых систем. Применяются в управляющих и дешифрующих устройствах.

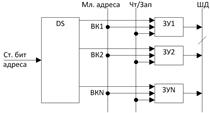

57. Вертикальное наращивание памяти (схема) и его назначение.

Вертикальное наращивание используется для увеличения адресуемого пространства ЗУ.

58. Горизонтальное наращивание памяти (схема) и его назначение.

Горизонтальное наращивание используется для увеличения разрядности ОЗУ.

Из каких шин состоит системная магистраль?

Системная магистраль включает в себя три многоразрядные шины:

– шину данных – служит для пересылки данных между ЦП и памятью или ЦП и устройствами ввода/вывода.

– шину адреса – служит для выбора устройств или ячеек памяти, куда пересылаются или откуда считываются данные по шине данных. Однонаправленная шина.

– шину управления – служит для передачи управляющих сигналов, определяющих характер обмена информацией по магистрали, предназначенных памяти и устройствам ввода/вывода.

Последнее изменение этой страницы: 2017-05-04; Просмотров: 3502; Нарушение авторского права страницы

Современные внутренние шины – смена приоритетов!

Среди наиболее динамично развивающихся областей компьютерной техники стоит отметить сферу технологий передачи данных: в отличие от сферы вычислений, где наблюдается продолжительное и устойчивое развитие параллельных архитектур, в «шинной» 1 сфере, как среди внутренних, так и среди периферийных шин, наблюдается тенденция перехода от синхронных параллельных шин к высокочастотным последовательным. (Заметьте, «последовательные» – не обязательно значит «однобитные», здесь возможны и 2, и 8, и 32 бит ширины при сохранении присущей последовательным шинам пакетной передачи данных, то есть в пакете импульсов данные, адрес, CRC и другая служебная информация разделены на логическом уровне 2 ).

1 Компьютерная шина (магистраль передачи данных между отдельными функциональными блоками компьютера) – совокупность сигнальных линий, объединённых по их назначению (данные, адреса, управление), которые имеют определённые электрические характеристики и протоколы передачи информации. Шины отличаются разрядностью, способом передачи сигнала (последовательные или параллельные), пропускной способностью, количеством и типами поддерживаемых устройств, протоколом работы, назначением (внутренняя, интерфейсная).

Шины могут быть синхронными (осуществляющими передачу данных только по тактовым импульсам) и асинхронными (осуществляющими передачу данных в произвольные моменты времени), а также могут использовать мультиплексирование (передачу адреса и данных по одним и тем же линиям) и различные схемы арбитража (то есть способа совместного использования шины несколькими устройствами).

2 Основным отличием параллельных шин от последовательных является сам способ передачи данных. В параллельных шинах понятие «ширина шины» соответствует её разрядности – количеству сигнальных линий, или, другими словами, количеству одновременно передаваемых («выставляемых на шину») битов информации. Сигналом для старта и завершения цикла приёма/передачи данных служит внешний синхросигнал. В последовательных же каналах передачи используется одна сигнальная линия (возможно использование двух отдельных каналов для разделения потоков приёма-передачи). Соответственно, информационные биты здесь передаются последовательно. Данные для передачи через последовательную шину облекаются в пакеты (пакет – единица информации, передаваемая как целое между двумя устройствами), в которые, помимо собственно полезных данных, включается некоторое количество служебной информации: старт-биты, заголовки пакетов, синхросигналы, биты чётности или контрольные суммы, стоп-биты и т. п. Но в свете последних достижений в «железной» сфере компьютерной индустрии малое количество сигнальных линий и логически более сложный механизм передачи данных последовательных шин оборачиваются для них существенным преимуществом – возможностью практически безболезненного наращивания рабочих частот в таких пределах, каких никогда не достичь громоздким параллельным шинам с их высокочастотными проблемами ожидания доставки каждого бита к месту назначения. Проблема в том, что каждая линия такой шины имеет свою длину, свою паразитную ёмкость и индуктивность и, соответственно, своё время прохождения сигнала от источника к приёмнику, который вынужден выжидать дополнительное время для гарантии получения данных по всем линиям. Так, к примеру, каждый байт, передаваемый через линк шины PCIExpress, для увеличения помехозащищённости «раздувается» до 10 бит, что, однако, не мешает шине передавать до 0,25 ГБ за секунду по одной паре проводов. Да, ширина последовательной шины на самом деле является количеством одновременно задействованных отдельных последовательных каналов передачи.

Все эти нововведения и смена приоритетов преследуют в конечном итоге одну цель – повышение суммарного быстродействия системы, ибо не все существующие архитектурные решения способны эффективно масштабироваться. Несоответствие пропускной способности шин потребностям обслуживаемых ими устройств приводит к эффекту «бутылочного горлышка» и препятствует росту быстродействия даже при дальнейшем увеличении производительности вычислительных компонентов – процессора, оперативной памяти, видеосистемы и так далее.

Процессорная шина

Любой процессор архитектуры x86CPU обязательно оснащён процессорной шиной. Эта шина служит каналом связи между процессором и всеми остальными устройствами в компьютере: памятью, видеокартой, жёстким диском и так далее. Так, классическая схема организации внешнего интерфейса процессора (используемая, к примеру, компанией Intel в своих процессорах архитектуры х86) предполагает, что параллельная мультиплексированная процессорная шина, которую принято называть FSB (Front Side Bus), соединяет процессор (иногда два процессора или даже больше) и контроллер, обеспечивающий доступ к оперативной памяти и внешним устройствам. Этот контроллер обычно называют северным мостом , он входит в состав набора системной логики ( чипсета ).

Используемая Intel в настоящее время эволюция FSB – QPB , или Quad-Pumped Bus, способна передавать четыре блока данных за такт и два адреса за такт! То есть за каждый такт синхронизации шины по ней может быть передана команда либо четыре порции данных (напомним, что шина FSB–QPB имеет ширину 64 бит, то есть за такт может быть передано до 4х64=256 бит, или 32 байт данных). Итого, скажем, для частоты FSB, равной 200 МГц, эффективная частота передачи адреса для выборки данных будет эквивалентна 400 МГц (2х200 МГц), а самих данных – 800 МГц (4х200 МГц) 3 .

3 Кстати, именно результирующей «учетверённой» частотой передачи данных (как и в случае с «удвоенной» передачей DDR-шины, где данные передаются дважды за такт) хвастаются производители и продавцы, умалчивая тот факт, что для многочисленных мелких запросов, где данные в большинстве своём умещаются в одну 64-байтную порцию (и, соответственно, не используются возможности DDR или QDR/QPB), на чтение/запись важнее именно частота тактирования.

В архитектуре же AMD64 (и её микроархитектуре K8), используемой компанией AMD в своих процессорах линеек Athlon 64/Sempron/Opteron, применён революционно новый подход к организации интерфейса центрального процессора – здесь имеет место наличие в самом процессоре нескольких отдельных шин. Одна (или две – в случае двухканального контроллера памяти) шина служит для непосредственной связи процессора с памятью, а вместо процессорной шины FSB и для сообщения с другими процессорами используются высокоскоростные шины HyperTransport. Преимуществом данной схемы является уменьшение задержек (латентности) при обращении процессора к оперативной памяти, ведь из пути следования данных по маршруту «процессор – ОЗУ» (и обратно) исключаются такие весьма загруженные элементы, как интерфейсная шина и контроллер северного моста.

Различия реализации классической архитектуры и АМD-K8

Различия реализации классической архитектуры и АМD-K8

Ещё одним довольно заметным отличием архитектуры К8 является отказ от асинхронности, то есть обеспечение синхронной работы процессорного ядра, ОЗУ и шины HyperTransport, частоты которых привязаны к «шине» тактового генератора (НТТ), которая в этом случае является опорной. Таким образом, для процессора архитектуры К8 частоты ядра и шины HyperTransport задаются множителями по отношению к НТТ, а частота шины памяти выставляется делителем от частоты ядра процессора 4

4 Пример: для системы на базе процессора Athlon 64-3000+ (1,8 ГГц) с установленной памятью DDR-333 стандартная частота ядра (1,8 ГГц) достигается умножением на 9 частоты НТТ, равной 200 МГц, стандартная частота шины HyperTransport (1 ГГц) – умножением НТТ на 5, а частота шины памяти (166 МГц) – делением частоты ядра на 11.

В классической же схеме с шиной FSB и контроллером памяти, вынесенным в северный мост, возможна (и используется) асинхронность шин FSB и ОЗУ, а опорной частотой для процессора выступает частота тактирования 5 (а не передачи данных) шины FSB, частота же тактирования шины памяти может задаваться отдельно. Из наиболее свежих чипсетов возможностью раздельного задания частот FSB и памяти обладает NVIDIA nForce 680i SLI, что делает его отличным выбором для тонкой настройки системы (разгона).

Что такое процессорная шина

Процессорная (иначе — системная) шина, которую чаще всего называют FSB (Front Side Bus), представляет собой совокупность сигнальных линий, объединенных по своему назначению (данные, адреса, управление), которые имеют определенные электрические характеристики и протоколы передачи информации.

Таким образом, FSB выступает в качестве магистрального канала между процессором (или процессорами) и всеми остальными устройствами в компьютере: памятью, видеокартой, жестким диском и так далее.

Непосредственно к системной шине подключен только CPU, остальные устройства подсоединяются к ней через специальные контроллеры, сосредоточенные в основном в северном мосте набора системной логики (чипсета) материнской платы.

Хотя могут быть и исключения – так, в процессорах AMD семейства К8 контроллер памяти интегрирован непосредственно в процессор, обеспечивая, тем самым, гораздо более эффективный интерфейс память-CPU, чем решения от Intel, сохраняющие верность классическим канонам организации внешнего интерфейса процессора.

Основные параметры FSB некоторых процессоров:

Intel Pentium III: 100/133; AGTL+; 800/1066

Intel Pentium 4: 100/133/200; QPB; 3200/4266/6400

Intel Pentium D: 133/200; QPB; 4266/6400

Intel Pentium 4 EE: 200/266; QPB; 6400/8533

Intel Core: 133/166; QPB; 4266/5333

Intel Core 2: 200/266; QPB; 6400/8533

AMD Athlon: 100/133; EV6; 1600/2133

AMD Athlon XP: 133/166/200; EV6; 2133/2666/3200

AMD Sempron: 800; HyperTransport; 6400

AMD Athlon 64: 800/1000; HyperTransport; 6400/8000

* Процессор: частота FSB МГц; тип FSB; теоретическая пропускная способность FSB Мб/с

Процессоры компании Intel используют системную шину QPB (Quad Pumped Bus), передающую данные четыре раза за такт, тогда как системная шина EV6 процессоров AMD Athlon и Athlon XP передает данные два раза за такт (Double Data Rate).

В архитектуре AMD64, используемой компанией AMD в процессорах линеек Athlon 64/FX/Opteron, применен новый подход к организации интерфейса CPU — здесь вместо процессорной шины FSB и для сообщения с другими процессорами используется:

высокоскоростная последовательная (пакетная) шина HyperTransport, построенная по схеме Peer-to-Peer (точка-точка), обеспечивающая высокую скорость обмена данными при сравнительно низкой латентности.